Page 1 / 36

**Rev 2.0**

# SafeSPI - Serial Peripheral Interface for Automotive Safety

Technical Specification

Page 2 / 36

**Rev 2.0**

| 1 INIT  | RODUCTION                                                                                  | 4  |

|---------|--------------------------------------------------------------------------------------------|----|

| 1.1 Red | quirement specification types                                                              | 4  |

| 1.2 Sco | ре                                                                                         | 4  |

| 2 OVE   | RVIEW ABOUT SPI COMMUNICATION                                                              | 5  |

| 3 PHY   | SICAL LAYER SPECIFICATION                                                                  | 7  |

| 3.1 Vol | tage levels and capacitances                                                               | 7  |

| 3.2 Tim | ning specifications                                                                        | 9  |

| 4 LOG   | ICAL LAYER                                                                                 | 13 |

| 4.1 Ge  | neral layer description                                                                    | 13 |

| 4.2 Log | cical layer implementation variants                                                        | 14 |

| 4.3 32E | Bit Frame                                                                                  | 15 |

| 4.3.1   | 32Bit Out of Frame <32oof> Flexible Data format <flexframe></flexframe>                    | 16 |

| 4.3.2   | 32Bit Out of Frame <32oof> Fixed sensor frame format <fixedsensorframe></fixedsensorframe> | 16 |

| 4.3.3   | 32Bit In Frame <32if> Flexible Data format <flexframe></flexframe>                         | 17 |

| 4.3.4   | 32Bit Description of frame bits (out-of-frame and in-frame)                                | 18 |

| 4.3.5   | 32Bit CRC Definition                                                                       | 21 |

| 4.3.6   | 32Bit Example of Fault management (out-of-frame and in-frame)                              | 23 |

| 4.4 48E | Bit Frame                                                                                  | 24 |

| 4.4.1   | 48Bit Out of Frame <48oof> Flexible Sensor Frame format <flexframe></flexframe>            | 24 |

| 4.4.2   | 48Bit Out of Frame <48oof> Fixed Sensor Frame format <fixedsensorframe></fixedsensorframe> | 26 |

| 4.4.3   | 48Bit Description of frame bits                                                            | 28 |

| 4.4.4   | 48Bit frame CRC Definition                                                                 | 30 |

| 4.4.5   | 48Bit Example of Fault management (out-of-frame and in-frame)                              | 31 |

Technical Specification

Rev 2.0

Page 3 / 36

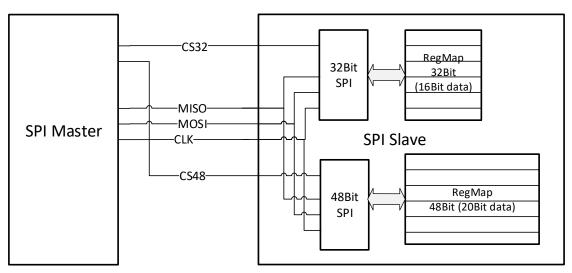

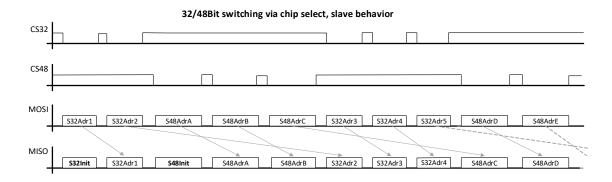

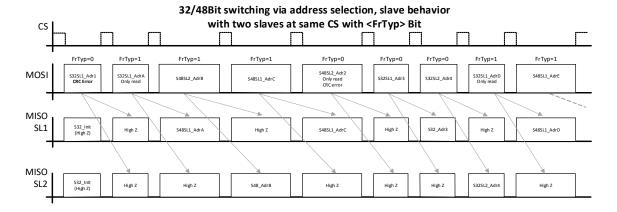

| 4.5 | 481 | Bit and 32Bit support in same Slave                                                       | 31 |

|-----|-----|-------------------------------------------------------------------------------------------|----|

| 4.  | 5.1 | Selection of 32Bit and 48Bit Mode by CS signal <selbitwidthbycs></selbitwidthbycs>        | 31 |

| 4.  | 5.2 | Selection of 32Bit and 48Bit Mode by sensor address <selbitwidthbyadr></selbitwidthbyadr> | 32 |

| 4.6 | Exa | ample for the use of the target and source address                                        | 34 |

| 5   | СНА | NGE HISTORY (MAIN CHANGES BETWEEN 1P0 AND 2P0)                                            | 36 |

Page 4 / 36

**Rev 2.0**

#### 1 Introduction

INFO\_001 The serial peripheral interface (SPI) is a synchronous serial communication interface used for short distance communication, usually between devices on a printed board assembly. The interface was developed by Motorola and is now a de-facto standard for several automotive applications.

Because there is no formal SPI standard, a wide variety of protocol options exist. This flexibility means every device defines its own protocol, increasing the development effort of new systems, devices and software.

In automotive safety applications, there is often an independent monitoring device (often termed "safing") which listens to sensor data on the SPI bus. This monitoring device is usually implemented in hardware and imposes constraints on the SPI protocol.

This specification describes a standard for a target SPI interface used in automotive applications. Its main focus is the transmission of sensor data between different devices.

#### 1.1 Requirement specification types

DEF\_002 Each requirement within this specification is marked with a unique identification. The identification consists of a classifier and a unique number. The number is unique over all versions of this specification. The classifiers are the following:

INFO: The following content has informative character.

DEF: The following content represents a definition. A definition itself cannot be fulfilled alone. However, other requirements refer to this definition and to fulfil these requirements, this definition must be followed

REQ: The following content is a requirement to the slaves and the masters

REQM: The following content is defined by SPI master, but needs to be respected by other bus participants

REQS: The following content is defined by SPI slave, but needs to be respected by other bus participants

REQL: The following content is defined by SPI monitor (Listener), but needs to be respected by other bus participants

Headings do not present any kind of requirement.

#### 1.2 Scope

DEF\_004 This SafeSPI standard targets automotive SPI devices. The main focus is sensors, interface integrated circuits (ICs), system application specific ICs (ASICs) and microcontrollers.

INFO\_005 Other devices may call themselves "SafeSPI compatible" according to REQ\_003 if wished.

Technical Specification SafeSPI\_Draft.docx 26 March 2021

Page 5 / 36

**Rev 2.0**

#### 2 Overview about SPI communication

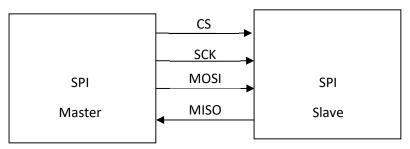

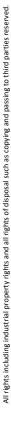

INFO\_006 A standard SPI interface consists of 4 ports as shown in Figure 1.

Figure 1 SPI-Interface

The Serial Clock (SCK) represents the master clock signal. This clock determines the speed of data transfer and all receiving and sending is done synchronously to this clock. The Chip Select (CS) activates the SPI interface at the SPI. As long as the CS signal is at high level, the SPI Slave will not accept the SCK signal or the Master-Out-Slave-In input (MOSI), and the Master-In-Slave-Out output (MISO) is in high impedance. When the CS signal is at low level, data can be transferred from the SPI Master to the SPI Slave and vice versa. Commands are transmitted through the MOSI to the SPI Slave and the SPI Slave returns its response through the MISO.

REQL\_006a On the monitor device, all signals (CSx, SCK, MOSI, MISO) are inputs only.

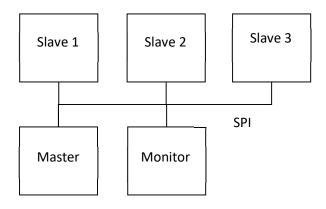

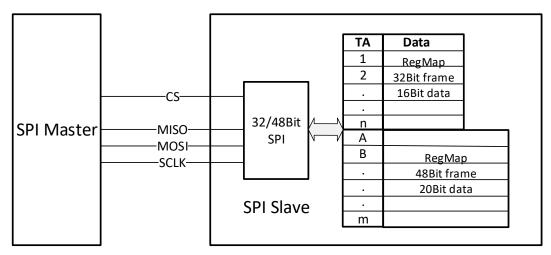

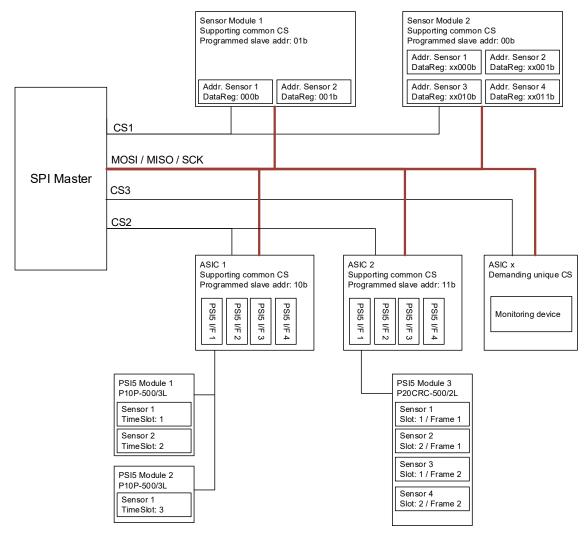

INFO\_007 SPI bus systems support several slave devices on one bus by using either multiple chip select lines, one for each slave, or by a logical addressing with only one common CS. For several airbag and safety systems a monitor device is connected as listener to the bus. This device is often an ASIC which needs a dedicated SPI format. An example configuration is depicted in Figure 2.

Figure 2 Typical SafeSPI system configuration

Specification

**Rev 2.0**

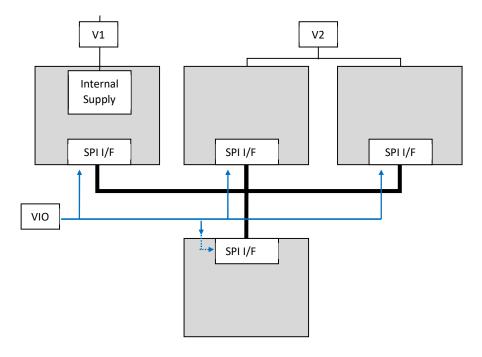

INFO\_008 The power supplies for each device on the SafeSPI bus are not specified, and can be independent, as shown in the figure below.

Figure 3 Example of different power domains V1, V2 & V3 with common VIO

Page 7 / 36

**Rev 2.0**

# 3 Physical layer specification

INFO\_010 The following chapter describes the physical layer of the SafeSPI specification. Besides voltage and current levels, capacitances of pins, the timings of the different communication lines are described.

#### 3.1 Voltage levels and capacitances

- *INFO\_011* Each of the devices can be powered from an independent supply. However, the SPI interface circuit of each device is supplied by a common VIO.

- *DEF\_012* VIO defines the supply voltage of the SPI interface of the device in order to have common reference for voltage input / output levels.

A supply voltage of a SafeSPI component may have tighter specification.

Positive current flows into the device.

|         | Parameter                                                                                            | Symbol          | Condition | Min | Max | Unit |

|---------|------------------------------------------------------------------------------------------------------|-----------------|-----------|-----|-----|------|

| REQ_013 | Mode 3.3V: Supply voltage of SPI interface (to be provided and required respectively at the VIO pin) | V <sub>IO</sub> |           | 3.0 | 3.6 | V    |

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

Page 8 / 36

**Rev 2.0**

*DEF\_013a* The following requirements apply to all four communication PINs, namely MISO, MOSI, CS and SCK if not noted otherwise.

| ID                     | Parameter                                                                                | Symbol               | Condition                                                               | Min                 | Max                 | Unit |

|------------------------|------------------------------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------|---------------------|---------------------|------|

| REQ_014                | Input / output capacitance                                                               | C <sub>IO</sub>      | -                                                                       | -                   | 10                  | pF   |

| REQ_015a               | Total signal load capacitance, <wide> range (1)</wide>                                   | $C_{LWide}$          | -                                                                       | 10                  | 100                 | pF   |

| REQ_015b               | Total signal load capacitance, <narrow> range (1)</narrow>                               | C <sub>LNarrow</sub> | -                                                                       | 30                  | 100                 | рF   |

| REQ_016                | Input low voltage                                                                        | V <sub>IL</sub>      | -                                                                       | 0                   | 0.3*V <sub>IO</sub> | V    |

| REQ_017                | Input high voltage                                                                       | V <sub>IH</sub>      | -                                                                       | 0.7*V <sub>IO</sub> | V <sub>IO</sub>     | V    |

| REQ_018                | Output low voltage                                                                       | V <sub>OL</sub>      | I <sub>LOA D</sub> = 1 mA                                               | 0                   | 0.1*V <sub>IO</sub> | V    |

| REQ_019                | Output high voltage                                                                      | V <sub>OH</sub>      | I <sub>LOAD</sub> = -1 mA                                               | 0.9*V <sub>IO</sub> | V <sub>IO</sub>     | V    |

| REQ_020                | Input voltage hysteresis                                                                 | V <sub>HYST</sub>    | -                                                                       | 0.1*V <sub>IO</sub> | -                   | V    |

| REQS_021               | Output leakage<br>current in case MISO<br>is in high impedance<br>(tri -state) condition | I <sub>LEAK</sub>    | @ V <sub>MISO</sub> forced to V <sub>IO</sub> /2                        | -10                 | 10                  | μА   |

| REQS_022<br>REQL_161   | Input pull-up current (2)                                                                | I <sub>PU</sub>      | CS only<br>@ V <sub>CS</sub> 0V V <sub>IHMin</sub>                      | -70                 | -20                 | μΑ   |

| REQS_022a<br>REQL_161a | Input pull-up<br>resistance (2)                                                          | R <sub>PU</sub>      | CS only<br>@ V <sub>CS</sub> 0V V <sub>IHMin</sub>                      | 60                  | 140                 | KOhm |

| REQS_023<br>REQL_162   | Input pull-down current (3)                                                              | I <sub>PD</sub>      | MOSI and SCK @ V <sub>MOSI/SCK</sub> V <sub>ILMax</sub> V <sub>IO</sub> | 20                  | 70                  | μΑ   |

| REQS_023a<br>REQL_162a | Input pull-down resistance (3)                                                           | R <sub>PD</sub>      | MOSI and SCK @ V <sub>MOSI/SCK</sub> V <sub>ILMax</sub> V <sub>IO</sub> | 60                  | 140                 | KOhm |

| REQM_164<br>REQL_165   | Input pull-down<br>current (3)                                                           | I <sub>PD</sub>      | MISO<br>@ V <sub>MISO</sub> V <sub>ILMax</sub> V <sub>IO</sub>          | 20                  | 70                  | μΑ   |

| REQM_164a<br>REQL_165a | Input pull-down resistance (3)                                                           | R <sub>PD</sub>      | MISO<br>@ V <sub>MISO</sub> V <sub>ILMax</sub> V <sub>IO</sub>          | 60                  | 140                 | KOhm |

**Rev 2.0**

#### Notes:

- (1) Either REQ\_015a or REQ\_015b shall be fulfilled as capacitive load range.

- (2) The pull-up at pin CS can be an active current source or a passive resistor.

- (3) The pull-down at pins SCK/MOSI/MISO can be an active current source or a passive resistor.

#### 3.2 Timing specifications

INFO\_024 The timings are specified to allow an operation of up to at least 10 MHz on the SPI. All timings are valid for the full range of specified voltage levels, input capacitances and current levels.

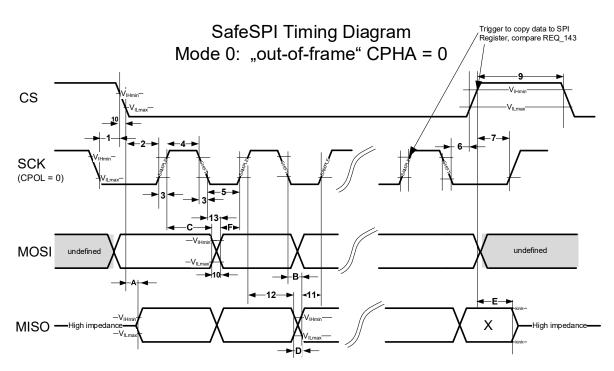

The different parameters are defined in the following figures 4 and figure 5.

DEF\_025

Figure 4 SPI timings for Mode 0: Out-of-frame / CPHA = 0

Page 10 / 36

**Rev 2.0**

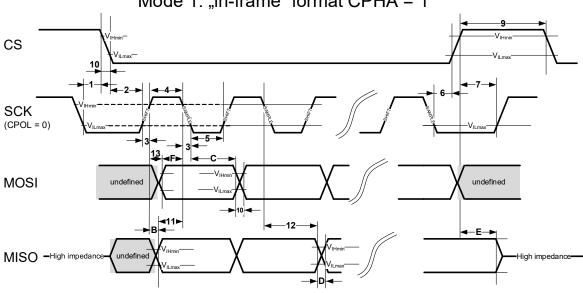

DEF\_025a

# SafeSPI Timing Diagram Mode 1: "in-frame" format CPHA = 1

Figure 5 SPI timings for Mode 1: In-frame / CPHA = 1

*DEF\_026* All timings are specified from V<sub>IHmin</sub> and V<sub>ILmax</sub> thresholds.

DEF\_027 All timings are specified over full voltage range of V<sub>IO</sub>, unless specified otherwise

DEF\_028 All timings are specified over full range of bus load C<sub>LWide</sub>, C<sub>LNarrow</sub>, unless specified otherwise

DEF\_029 All timings are specified over full temperature range defined by the unit for which the SafeSPI block is implemented, unless specified otherwise

*INFO\_030* The following requirements are to the slave and listener from master point of view:

| ID                   | Parameter                                | Symbol | Condition | Min | Max | Unit |

|----------------------|------------------------------------------|--------|-----------|-----|-----|------|

| REQS_031             | MISO data valid time (CS)                | Α      | -         | -   | 40  | ns   |

| REQS_032             | MISO data valid time (SCK)               | В      | -         | ı   | 32  | ns   |

| REQS_051<br>REQL_158 | MOSI data hold time                      | С      | -         | 20  | -   | ns   |

| REQS_034             | MISO rise/fall time<br>see also INFO_037 | D      | -         | 2   | 9   | ns   |

| REQS_035             | MISO data disable lag time               | E      | -         | 1   | 50  | ns   |

| REQS_050<br>REQL_157 | MOSI data setup time                     | F      | -         | 10  | -   | ns   |

Page 11 / 36

**Rev 2.0**

INFO\_037 MISO rise/fall time is not defined during transition between high impedance and active mode

INFO\_038 To cover the specified range of parameter <B> and <D> for the specified signal load capacitance ranges, a user programmable drive strength implementation and/or a slew rate controlled driver output is recommended. In case programable driver strength is used there shall be an overlap of at least 20% relative to the respective range step. (e.g. at the range switching point of 60pF the lower range should go up to 66pF while the upper range should go down to 54pF)

*INFO\_039* The following requirements are to the master and listener from slave point of view:

| ID                   | Parameter                                                                               | Symbol | Condition | Min   | Max  | Unit |

|----------------------|-----------------------------------------------------------------------------------------|--------|-----------|-------|------|------|

| REQM_150             | SCK operating frequency                                                                 | -      | -         | 0.095 | 10.5 | MHz  |

| REQM_040             | SCK disable lead time                                                                   | 1      | -         | 10    | -    | ns   |

| REQM_041             | SCK enable lead time                                                                    | 2      | -         | 40    | -    | ns   |

| REQM_042             | SCK rise and fall time                                                                  | 3      | -         | 2     | 9    | ns   |

| REQM_043             | SCK high time                                                                           | 4      | -         | 37    | -    | ns   |

| REQM_044             | SCK low time                                                                            | 5      | -         | 37    | -    | ns   |

| REQM_045             | SCK enable lag time                                                                     | 6      | -         | 20    | -    | ns   |

| REQM_046             | SCK disable lag time                                                                    | 7      | -         | 10    | -    | ns   |

| REQM_047             | Sequential transfer delay<br>(Out-Of-Frame) in case of<br>MOSI Write commands<br>(RW=1) | 9      | -         | 750   | -    | ns   |

| REQM_047a            | Sequential transfer delay<br>(Out-Of-Frame) in case of<br>MOSI Read commands<br>(RW=0)  | 9      | -         | 450   | -    | ns   |

| REQM_048             | Sequential transfer delay (In-Frame)                                                    | 9      | -         | 200   | -    | ns   |

| REQM_049             | MOSI rise and fall time                                                                 | 10     | -         | 2     | 9    | ns   |

| REQM_152<br>REQL_153 | MISO data setup time                                                                    | 11     | -         | 5     | -    | ns   |

| REQM_053<br>REQL_154 | MISO data hold time                                                                     | 12     | -         | Х     | -    | ns   |

Technical Specification SafeSPI\_Draft.docx 26 March 2021

Page 12 / 36

**Rev 2.0**

| ID       | Parameter             | Symbol | Condition | Min | Max | Unit |

|----------|-----------------------|--------|-----------|-----|-----|------|

| REQM_151 | MOSI valid time       | 13     | -         | -   | 10  | ns   |

| REQM_122 | CS rise and fall time | 10     | -         | 2   | 9   | ns   |

DEF\_036 X: MISO data is guaranteed to be stable until the next SCK shift edge

INFO\_052 To cover the specified range of parameter <3> and <10> for the specified load capacitance range, a user programmable drive strength implementation and/or a slew rate controlled driver output is recommended. In case programable driver strength is used there shall be an overlap of at least 20% relative to the respective range step. (e.g. at the range switching point of 60pF the lower range should go up to 66pF while the upper range should go down to 54pF)

INFO\_053 To achieve the parameter 9, it takes more time for an Out-Of-Frame protocol since it has to prepare the correct data in between two frames.

Page 13 / 36

**Rev 2.0**

## 4 Logical layer

# 4.1 General layer description

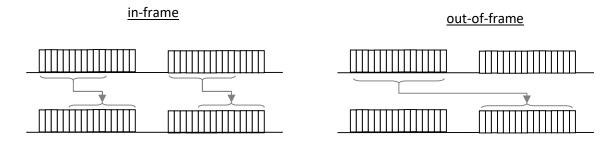

DEF\_054 There are 32Bit and 48Bit frame length supported. For 32Bit there is In-frame (if) and Out-Of-Frame (oof) communication supported while for 48Bit frame length only out-of-frame is defined. For In-Frame mode the data of the slave response is within the same time slot as the master's request while for the Out-Of-Frame the logical response of the slave is within the next frame of the master. Figure 6 depicts both options

Figure 6 in-frame and out-of-frame communication

- REQ\_055 The number of bits is 32Bit for SafeSPI2 <32... > variants and 48Bit for SafeSPI2 <48... > variants

- REQ 056 The MSB is transferred first within a frame.

- REQ\_143 For out of frame communication read commands, the slave internal data requested by read command is copied to the SPI register using either rising edge of chip select (CS) at the end of the read command or sampling phase of last SCK cycle, as trigger signal. Compare figure 4.

- INFO\_057 The 32Bit variants support an out-of-frame as well as an in-frame protocol. Both have the same CRC polynomial and two separate response frames, one for sensor data (identified by D=1) and one for other data (D=0). Sensor data can have up to 16bits.

The 48Bit variants supports only out-of-frame protocol. It supports also two different response frames, one for sensor data (identified by D=1) and one for other data (D=0). Sensor data can have up to 20bits.

REQ\_064 In case a slave receives a frame, he could not "understand" / "decode", the slave should respond accordingly to table §4.3.6 and §4.4.5 (Fault management), to avoid collision in case of multiple slave with common CS.

Page 14 / 36

**Rev 2.0**

# 4.2 Logical layer implementation variants

*INFO\_123* Following implementation variants are possible.

| ID       | SafeSPI  | Comment                                                                                                                                                                                                                             |

|----------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Variant  |                                                                                                                                                                                                                                     |

| REQ_003  | SafeSPI  | It supports as per SafeSPI 1p0 32Bit in- and out of frame communication                                                                                                                                                             |

| REQ_003a | SafeSPI2 | Functionality will be defined by implementation options.                                                                                                                                                                            |

|          |          | Bitwidth configuration.                                                                                                                                                                                                             |

|          |          | Either one of following options can be selected:                                                                                                                                                                                    |

|          |          | <32if>: 32Bit in frame communication                                                                                                                                                                                                |

|          |          | <32oof>: 32Bit out of frame communication                                                                                                                                                                                           |

|          |          | <32>: 32Bit in and out of frame communication are supported                                                                                                                                                                         |

|          |          | <48oof>: 48Bit out of frame communication                                                                                                                                                                                           |

|          |          | <48/32oof>: 32Bit and 48Bit frame are supported by single slave.                                                                                                                                                                    |

|          |          | The selection between the 32Bit and 48Bit can be done by either one or                                                                                                                                                              |

|          |          | both of following implementation options:                                                                                                                                                                                           |

|          |          | <selbitwidthbyadr>: Switching between 32/48Bit frame is done by MOSI</selbitwidthbyadr>                                                                                                                                             |

|          |          | Address (FrTyp Bit), compare section 4.5.2                                                                                                                                                                                          |

|          |          | <selbitwidthbycs>: Switching between 32/48Bit frame is done by CS</selbitwidthbycs>                                                                                                                                                 |

|          |          | signal for 32Bit and 48Bit frame, compare section 4.5.1                                                                                                                                                                             |

| REQ_003b | SafeSPI2 | Signal Frame Configuration.                                                                                                                                                                                                         |

|          |          | One out of the two options need to be selected:                                                                                                                                                                                     |

|          |          | <flexframe>: compatible to SafeSPI 1p0 Frame definition. Keeps</flexframe>                                                                                                                                                          |

|          |          | maximum flexibility in definition of functionality of MOSI and MISO                                                                                                                                                                 |

|          |          | frame while assuring that MISO frame can be monitored by Monitor                                                                                                                                                                    |

|          |          | devices (e.g. definition of <d>, <crc>, <data15:0>)</data15:0></crc></d>                                                                                                                                                            |

|          |          | <fixedsensorframe>: Additional bit positions are defined in order to</fixedsensorframe>                                                                                                                                             |

|          |          | allow standardized read/write communication. Note this frame is a                                                                                                                                                                   |

|          |          | further detailed definition of <flexframe>.</flexframe>                                                                                                                                                                             |

|          |          | devices (e.g. definition of <d>, <crc>, <data15:0>)  <fixedsensorframe>: Additional bit positions are defined in order to allow standardized read/write communication. Note this frame is a</fixedsensorframe></data15:0></crc></d> |

Page 15 / 36

Rev 2.0

| ID       | SafeSPI  | Comment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Variant  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| REQ_003c | SafeSPI2 | Slave Addressing:  One out of the five options need to be selected: <selslavebycs>: Slave is addressed by CS, meaning each slave needs to have separate CS signal.  <sel2slavebyadrpin> Max two Slaves can be addressed by TA9. TA on the slave is defined logic level at pin TA9.  <sel2slavebyadrnvm>: Max two Slaves can be addressed by TA9. TA9 is on slave side programmed as a fix address in nonvolatile memory of the slave.  <sel4slavebyadrpin> Max four Slaves can be addressed by TA9:8. TA on the slave is defined logic level at pins TA9 TA8.  <sel4slavebyadrnvm>: Max four Slaves can be addressed by TA9:8.  TA9:8 is on slave side programmed as a fix address in nonvolatile</sel4slavebyadrnvm></sel4slavebyadrpin></sel2slavebyadrnvm></sel2slavebyadrpin></selslavebycs> |

| REQ 003d | SafeSPI2 | memory of the slave.  Capacitive load Configuration.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NEQ_0030 | SalesPiz | Capacitive load configuration. <c<sub>LNarrow&gt;, <c<sub>LWide&gt; different capacitive loads ranges. Compare REQ_015.</c<sub></c<sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

## INFO\_138 Examples:

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

SafeSPI2 <32if>, <32oof>, <FlexFrame>, <SelSlaveByCS>, <Sel4SlaveByAdrPin>, < $C_{LWide}$  > => equal to SafeSPI 1p0 configuration.

SafeSPI2 <48/32oof>, <SelBitWidthByAdr>, <SelBitWidthByCS>; <FixedSensorFrame> <Sel2SlaveByAdrNVM> ; < $C_{LWide}$ >

=> supports 48- and 32Bit out of frame communication where switching between the 32Bit and the 48Bit can be alternatively done by separate chip select or MOSI address TA. Up to two slaves can be selected by address stored in NVM.

#### 4.3 32Bit Frame

- *INFO\_058* This section describes the logical encodings for the 32Bit variants.

- DEF\_059 Bits within the master request (MOSI) or the slave response (MISO) which are marked as '\*' can be freely defined and are not specified within this specification.

- *DEF\_060* A bit which is marked as '\$' within the slave response (MISO) represents a tri-state of the output pin (high impedance).

Page 16 / 36

**Rev 2.0**

#### 4.3.1 32Bit Out of Frame <32oof> Flexible Data format <FlexFrame>

REQ\_061 The following table shows the command frame format for the 32Bit out of frame with maximum flexibility. Note, this frame is compatible to SafeSPI1.

| Bit        | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20    | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2    | 1   | 0   |

|------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|

| MOSI TA9:0 |     |     |     |     |     |     |     |     |     |     | *   | FrTyp |     |     |     |     |     |     |     |     | *   |     |     |     |     |     |     |     | (   | 22:0 | ,   |     |

| value      | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 | 0/1 |

REQ\_062 The following table shows the response frame format for 32Bit out of frame with maximum flexibility. Note, this frame is compatible to SafeSPI1.

| Bit   | 31 | 30    | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12   | 11           | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|-------|----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|

| MISO  | D  | SA9:0 |     |     |     |     |     |     |     |     |     | S1  |     |     |     |     |     |     | 0   | DATA | <b>\15</b> : | 0   |     |     |     |     |     |     | S0  | (   | C2:0 |     |

| value | 1  | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1          | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 |

*REQ\_063* The following table shows the response frame format for the out-of-frame protocol for all other data.

| E | Bit  | 31        | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|---|------|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|

| ٨ | ЛISO | O D SA9:0 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     | 13  | *   |     |     |     |     |     |     |     |     | (   | C2:0 |     |

| ν | alue | 0         | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 |

4.3.2 32Bit Out of Frame <32oof> Fixed sensor frame format <FixedSensorFrame>

REQ\_127 The following table shows the command frame format for 32Bit out of frame with higher standardization level as <FlexFrame>

|   | Bit   | 31  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19    | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10   | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1    | 0   |

|---|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|

|   | MOSI  |     |     |     |     | TA  | 9:0 |     |     |     |     | RW  | САР | FrTyp |     |     |     |     |     |     | D   | ATA | 115: | 0   |     |     |     |     |     |     | (   | C2:( | )   |

| - | value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 |

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

Page 17 / 36

**Rev 2.0**

REQ\_128 The following table shows the response frame format for 32Bit out of frame optimized for <FixedSensorFrame>.

| Bit   | 31 | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0  |

|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|

| MISO  | D  |     |     |     |     | SA  | 9:0 |     |     |     |     | S1  |     |     |     |     |     |     | D   | ATA | 015 | :0  |     |     |     |     |     |     | S0  | (   | 2:0 |    |

| value | 1  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/ |

REQ\_129 The following table shows the response frame format for the out-of-frame protocol for all other data. (Fixed Sensor status frame)

| Bit   | 31 | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| MISO  | D  |     |     |     |     | SA  | 9:0 |     |     |     |     | *   |     |     |     |     |     |     | D.  | АТА | 015 | :0  |     |     |     |     |     |     | *   | (   | 2:0 |     |

| value | 0  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

4.3.3 32Bit In Frame <32if> Flexible Data format <FlexFrame>

REQ\_065 The following table shows the command frame format for the 32Bit in frame with maximum flexibility. Note, this frame is compatible to SafeSPI1.

| Bit   | 3  | 1  | 30  | 29  | 28  | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|-------|----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|-----|-----|-----|

| MOSI  |    |    | Т   | A9: | 5   |     |     |     |     |     |     |     |     |     |     |     | *   | k   |     |     |     |     |     |     |     |     |     |     | C   | C2:0 | )   | *   |     |

| value | 0, | /1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1  | 0/1 | 0/1 | 0/1 |

REQ\_066 The following table shows the response frame format for 32Bit in frame with maximum flexibility. Note, this frame is compatible to SafeSPI1.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26  | 25 | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|----|----|----|----|----|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| MISO  |    |    | \$ |    |    | *   | D  |     | S   | A9: | 5   |     |     |     |     |     |     |     | D   | ATA | 015 | 5:0 |     |     |     |     |     |     | S0  | С   | R2: | O   |

| value |    |    |    |    |    | 0/1 | 1  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

REQ\_067 The following table shows the other responses from a slave in the in-frame protocol.

| Bit   | 31 | 30 | 29 | 28 | 27 | 26  | 25 | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|----|----|----|----|----|-----|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| MISO  |    |    | \$ |    |    | *   | D  |     | S   | A9: | 5   |     |     |     |     |     |     |     |     |     | *   |     |     |     |     |     |     |     |     | (   | R2: | 0   |

| value |    |    |    |    |    | 0/1 | 0  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

Page 18 / 36

**Rev 2.0**

# 4.3.4 32Bit Description of frame bits (out-of-frame and in-frame)

| ID      | Symbol | Name                                                                                                                                                                                                      |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ_068 | TA9:0  | The target address (TA) is the command which defines the command to the sensor.                                                                                                                           |

|         |        | TA9:7 are mandatory slave internal address bits in case of<br><selslavebycs></selslavebycs>                                                                                                               |

|         |        | TA9:8 shall correspond to a programmable 2Bit slave address in case<br><sel4slavebyadrpin> or <sel4slavebyadrnvm> is used.<br/>TA7 is slave internal address bit.</sel4slavebyadrnvm></sel4slavebyadrpin> |

|         |        | TA9 shall correspond to a programmable 1Bit slave address in case<br><sel2slavebyadrpin> or <sel2slavebyadrnvm>. TA8:7 is slave<br/>internal address bit.</sel2slavebyadrnvm></sel2slavebyadrpin>         |

|         |        | TA6:0 are optional address bits.                                                                                                                                                                          |

| REQ_130 | RW     | Read/Write Bit                                                                                                                                                                                            |

|         |        | RW=0b read request, sensor provides with following frame data from requested address                                                                                                                      |

|         |        | RW=1b write request, device writes data of DATAI to address TA                                                                                                                                            |

| REQ_131 | CAP    | Capture mode; captures (freezes all sensor data channels) Optional functionality. If not implemented this bit positional shall be fixed 0b.                                                               |

|         |        | Allows to freeze/release all data channels under control of this bit. This allows to read sequentially different data channels while it is assured that the data of all channels is from same time stamp. |

Technical Specification

Page 19 / 36

**Rev 2.0**

| ID      | Symbol    | Name                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ_159 | FrTyp     | Frame type optional. Only used in case option <32/48oof> <selbitwidthbyadr> is implemented. Indicates to slave / listener whether MISO response in next frame shall be 32Bit or 48Bit. FrTyp = 0b next MISO frame is 32Bit frame FrTyp = 1b next MISO frame is 48Bit frame  Indicates to slave / listener whether next incoming MOSI frame shall be interpreted as 32Bit or 48Bit. Slave / listener uses CRC and Clock count information to detect MOSI frame format ClkCount = 32 and CRC3=OK received MOSI frame is interpreted as 32Bit frame - ClkCount = 48 and CRC8=OK received MOSI frame is interpreted as 48Bit frame</selbitwidthbyadr> |

|         |           | Alternatively slave / listener uses above FrTyp information<br><frtyp> = 0b next MOSI frame is 32Bit frame<br/><frtyp> = 1b next MOSI frame is 48Bit frame<br/>Note in case of MOSI CRC/CLK count error, slave / listener may use<br/><frtyp> information for the next frame even if CRC error is present while responding on MISO with communication error in next frame.<br/>Otherwise (no &lt;32/48oof&gt; <selbitwidthbyadr> option)<br/>FrTyp = free to use</selbitwidthbyadr></frtyp></frtyp></frtyp>                                                                                                                                       |

| REQ_133 | DATAI15:0 | Data written to address TA for RW=1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Technical Specification

Page 20 / 36

**Rev 2.0**

| ID      | Symbol | Name                                                                                                                                                                                                       |

|---------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ_069 | SA9:0  | The source address (SA) is the address uniquely identifying the content of the response data (DATAO15:0).                                                                                                  |

|         |        | SA9:7 are mandatory slave internal address bits in case of<br><selslavebycs></selslavebycs>                                                                                                                |

|         |        | SA9:8 shall correspond to a programmable 2Bit slave address in case<br><sel4slavebyadrpin> or <sel4slavebyadrnvm> are used. SA7 is<br/>slave internal address bit.</sel4slavebyadrnvm></sel4slavebyadrpin> |

|         |        | SA9 shall correspond to a programmable 1Bit slave address in case<br><sel2slavebyadrpin> or <sel2slavebyadrnvm>. SA8:7 is slave<br/>internal address bit.</sel2slavebyadrnvm></sel2slavebyadrpin>          |

|         |        | SA6:0 are optional address bits.                                                                                                                                                                           |

|         |        | Note: In-frame uses only SA9:5. Example for the use of SA7:0 for a PSI5 transceiver:                                                                                                                       |

|         |        | SA7:5 PSI5 channel                                                                                                                                                                                         |

|         |        | SA4:3 PSI5 time slot                                                                                                                                                                                       |

|         |        | SA2:0 PSI5 frame (see PSI5 V2.1 substandard Chassis and Safety)                                                                                                                                            |

| REQ_070 | D      | The sensor data bit identifying if response contains sensor data or not (i.e. identifying frame format for response.                                                                                       |

|         |        | D=0: no sensor data, e.g. status data or read back of configuration data                                                                                                                                   |

|         |        | D=1: sensor data format                                                                                                                                                                                    |

| REQ_071 | S1:0   | Out-of-frame format:                                                                                                                                                                                       |

|         |        | The sensor status bits describe the status of the sensor data within a data frame response.                                                                                                                |

|         |        | 00b: valid sensor data                                                                                                                                                                                     |

|         |        | 01b: Sensor in any error state DATAO15:0 may contain any kind of data                                                                                                                                      |

|         |        | 11b: sensor in init state; DATAO 15:0 contains sensor data                                                                                                                                                 |

|         |        | 10b: free to use                                                                                                                                                                                           |

Page 21 / 36

**Rev 2.0**

| ID       | Symbol    | Name                                                                                                                                                           |

|----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ_071a | S0        | In-frame format:                                                                                                                                               |

|          |           | The sensor status bit describes the status of the sensor data within a data frame response.                                                                    |

|          |           | 0b: valid sensor data                                                                                                                                          |

|          |           | 1b: Sensor in any error state or non sensor data available;                                                                                                    |

| REQ_071b | DATAO15:0 | Up to 16bit of sensor data given in 2 <sup>nd</sup> complement. If sensor data is less than 16bit, data should be aligned to MSB. Unused bits are free to use. |

| REQ_072  | C2:0      | CRC for out-of-frame command and response frames calculated over bit 31 to 3. See section 4.3.5 for details.                                                   |

| REQ_073  | CC2:0     | CRC for in-frame command frames calculated over bit 31 to 5. See section 4.3.5 for details.                                                                    |

| REQ_074  | CR2:0     | CRC for in-frame response frames calculated over bit 26 to 3. See section 4.3.5 for details.                                                                   |

# 4.3.5 32Bit CRC Definition

*REQ\_075* For the in-frame format a 3bit CRC with the polynomial  $0x5 (x^3 + x^1 + x^0)$  is used with a start value of 111b and a target value of 000b. Start value shall be added in front of MSB of SPI frame.

REQ\_076 For the out-of-frame format a 3bit CRC with the polynomial 0x5 ( $x^3 + x^1 + x^0$ ) is used with a start value of 101b and a target value of 000b. Start value shall be added in front of MSB of SPI frame.

INFO\_076a There are different conventions how to represent a polynomial in hexadecimal notation. The notation 0x5 in this document is a hexadecimal representation (Koopman notation) of the polynomial x3 + x1 + 1, using x3 as the highest bit and an implicit +1 term.

INFO\_077 Note that the bits over which the CRC is calculated is not equal for all frame formats. The following test cases can be used to verify the implementation. Different handling of start value can be used as long the same results are achieved as by putting start value in front of MSB.

| ID      | protocol                       | 32bit frame    | CRC result |

|---------|--------------------------------|----------------|------------|

| REQ_078 | out-of frame, command/response | 0x 00 00 00 03 | ОК         |

| REQ_079 | out-of frame, command/response | 0x FF FF FF F8 | OK         |

| REQ_080 | out-of frame, command/response | 0x 0F 0F 0F 0A | OK         |

Technical Specification SafeSPI\_Draft.docx 26 March 2021

Technical Specification

Page 22 / 36

**Rev 2.0**

| REQ_081 | out-of frame, command/response | 0x 0F F2 C8 FE | OK   |

|---------|--------------------------------|----------------|------|

| REQ_082 | in-frame, command              | 0x 00 00 00 04 | ОК   |

| REQ_083 | in-frame, command              | 0x FF FF FF F7 | ОК   |

| REQ_084 | in-frame, command              | 0x 0F 0F 0F 13 | OK   |

| REQ_085 | in-frame, command              | 0x 0F F2 C8 E7 | OK   |

| REQ_086 | in-frame, response             | 0x 00 00 00 06 | OK   |

| REQ_087 | in-frame, response             | 0x FF FF FF FC | OK   |

| REQ_088 | in-frame, response             | 0x 0F 0F 0F 0A | ОК   |

| REQ_089 | in-frame, response             | 0x 0F F2 C8 FE | ОК   |

| REQ_090 | all responses & commands       | 0x 00 00 00 00 | FAIL |

| REQ_091 | all responses & commands       | 0x FF FF FF FF | FAIL |

| REQ_092 | all responses & commands       | 0x 0F 0F 0F 0F | FAIL |

| REQ_093 | all responses & commands       | 0x 0F F2 C8 FA | FAIL |

Rev 2.0

# 4.3.6 32Bit Example of Fault management (out-of-frame and in-frame)

INFO\_139

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

|                                           | In-frame                                                                                          | <32if>                                                                                                                                                                          | Out-of-fram                                                                                       | e <32oof>                                          |

|-------------------------------------------|---------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|----------------------------------------------------|

| Fault                                     | with common CS<br><selslavebyadrpin><br/><selslavebyadrnvm></selslavebyadrnvm></selslavebyadrpin> | with dedicated CS<br><selslavebycs></selslavebycs>                                                                                                                              | with common CS<br><selslavebyadrpin><br/><selslavebyadrnvm></selslavebyadrnvm></selslavebyadrpin> | with dedicated CS<br><selslavebycs></selslavebycs> |

| MOSI CRC Error                            | last bit of CR2:0 to be intentionally wrong)                                                      | nverted by slave (CRC                                                                                                                                                           | High impedance of MISO (in next frame)                                                            | MISO shall return<br>an error indication*          |

| SCK cycle no equal<br>to 32 (including 0) | No reaction of slave possible. CRC might be wrong depending on number of bit missing or added     | No reaction of slave possible. CRC might be wrong depending on number of bit missing or added.  Error indication (or information should be given in the next frame if possible) | High impedance of<br>MISO (in next frame)                                                         | MISO shall return<br>an error indication*          |

| TA9:8 (Slave<br>Address)                  | High impedance of<br>MISO (in answer<br>frame)                                                    | NA                                                                                                                                                                              | High impedance of<br>MISO (in next frame)                                                         | NA                                                 |

| TA7:0 (for all supported bits)            | MISO shall return an error indication*                                                            | NA                                                                                                                                                                              | MISO shall return an error indication*                                                            | NA                                                 |

| TA7:0 (for all supported bits)            | NA                                                                                                | MISO shall return<br>an error indication*                                                                                                                                       | NA                                                                                                | MISO shall return<br>an error indication*          |

| Module internal<br>error                  | MISO shall return an ei<br>(no answer)                                                            | rror indication (prefera                                                                                                                                                        | ble) if possible, if not pos                                                                      | sible high impedance                               |

NA: not applicable

- \*) Error indication can be either one of:

- status bits (S1:0)

- high impedance of MISO (in next frame)

- any other mean

Page 24 / 36

**Rev 2.0**

# 4.4 48Bit Frame

- *INFO\_096* This section describes the logical encodings for the 48Bit protocol options.

- DEF\_097 Bits within the master request (MOSI) or the slave response (MISO) which are marked as '\*' can be freely defined and are not specified within this specification.

- 4.4.1 48Bit Out of Frame <48oof> Flexible Sensor Frame format <FlexFrame>

- REQ\_099 The following table shows the command frame format for the out-of-frame protocol

| Bit   | 47  | 46    | 45  | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35    | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|

| MOSI  |     | TA9:0 |     |     |     |     |     |     |     |     |     | *   | FrTyp |     |     |     | *   |     |     |     |

| value | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| MOSI  |     |     |     |     |     |     |     |     |     | *   | k   |     |     |     |     |     |     |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| моѕі  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

*REQ\_100* The following table shows the response frame format for the out-of-frame protocol in case of sensor data is transferred.

| Bit   | 47 | 46  | 45    | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35  | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| мiso  | D  |     | SA9:0 |     |     |     |     |     |     |     |     |     | k   | S1  | .:0 |     |     | *   |     |     |

| value | 1  | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26        | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-------|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     | DATAO19:0 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| value | 0/1 | 0/1       | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

Technical Specification SafeSPI\_Draft.docx 26 March 2021

Page 25 / 36

**Rev 2.0**

REQ\_101 The following table shows the response frame format for the out-of-frame protocol for all other data.

| Bit   | 47 | 46  | 45  | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35  | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| мiso  | D  |     |     |     |     | SA  | 9:0 |     |     |     |     |     |     |     |     | *   |     |     |     |     |

| value | 0  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26  | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     |     |     |     |     |     |     |     |     | ,   | k   |     |     |     |     |     |     |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

Page 26 / 36

**Rev 2.0**

# 4.4.2 48Bit Out of Frame <48oof> Fixed Sensor Frame format <FixedSensorFrame>

# REQ\_135 The following table shows the command frame format for the out-of-frame protocol

| Bit   | 47  | 46    | 45  | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35    | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-------|-----|-----|-----|-----|-----|-----|-----|

| MOSI  |     | TA9:0 |     |     |     |     |     |     |     |     |     | CAP | FrTyp |     |     |     | *   |     |     |     |

| value | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26        | 25  | 24  | 23  | 22  | 21  | 20  | 19  | 18  | 17  | 16  | 15  | 14  | 13  | 12  | 11  | 10  | 9   | 8   |

|-------|-----|-----------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| моѕі  |     | DATAI19:0 |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |     |

| value | 0/1 | 0/1       | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| моѕі  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

# *REQ\_136* The following table shows the response frame format for the out-of-frame protocol in case of sensor data is transferred.

| Bit   | 47 | 46  | 45  | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35  | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| MISO  | D  |     |     |     |     | SA  | 9:0 |     |     |     |     | IDS | CE  | S1  | .:0 |     | DC  | nt  |     | *   |

| value | 1  | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26                                      | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|-------|-----|-----------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|

| MISO  |     | DATAO19:0                               |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |

| value | 0/1 | 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

All rights including industrial property rights and all rights of disposal such as copying and passing to third parties reserved.

Page 27 / 36

**Rev 2.0**

REQ\_137 The following table shows the response frame format for the out-of-frame protocol for all other data.

| Bit   | 47 | 46  | 45    | 44  | 43  | 42  | 41  | 40  | 39  | 38  | 37  | 36  | 35  | 34  | 33  | 32  | 31  | 30  | 29  | 28  |

|-------|----|-----|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| мiso  | D  |     | SA9:0 |     |     |     |     |     |     | *   | CE  | S1  | :0  |     |     | *   |     |     |     |     |

| value | 0  | 0/1 | 0/1   | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

| Bit   | 27  | 26                                       | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 |

|-------|-----|------------------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|

| міѕо  |     | DATAO19:0                                |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |

| value | 0/1 | 1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/1 0/ |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |

| Bit   | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| міѕо  |     |     |     | C7  | ':0 |     |     |     |

| value | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 | 0/1 |

Page 28 / 36

**Rev 2.0**

# 4.4.3 48Bit Description of frame bits

| ID      | Symbol | Name                                                                                                                                                                                                      |

|---------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REQ_105 | TA9:0  | The target address (TA) is the command which defines the command to the sensor.                                                                                                                           |

|         |        | TA9:7 are mandatory slave internal address bits in case of<br><selslavebycs></selslavebycs>                                                                                                               |

|         |        | TA9:8 shall correspond to a programmable 2Bit slave address in case <sel4slavebyadrpin> or <sel4slavebyadrnvm> is used. TA7 is slave internal address bit.</sel4slavebyadrnvm></sel4slavebyadrpin>        |

|         |        | TA9 shall correspond to a programmable 1Bit slave address in case <sel2slavebyadrpin> or <sel2slavebyadrnvm>. TA8:7 is slave internal address bit.</sel2slavebyadrnvm></sel2slavebyadrpin>                |

|         |        | TA6:0 are optional address bits.                                                                                                                                                                          |

| REQ_107 | RW     | Read/Write Bit                                                                                                                                                                                            |

|         |        | RW=0b read request, sensor provides with following frame data from requested address                                                                                                                      |

|         |        | RW=1b write request, device writes data of DATAI to address TA9                                                                                                                                           |

| REQ_106 | SA9:0  | The source address (SA) is the address uniquely identifying the content of the response data (DATAO19:0).                                                                                                 |

|         |        | SA9:7 are mandatory slave internal address bits in case of<br><selslavebycs></selslavebycs>                                                                                                               |

|         |        | SA9:8 shall correspond to a programmable 2Bit slave address in case <sel4slavebyadrpin> or <sel4slavebyadrnvm> are used. SA7 is slave internal address bit.</sel4slavebyadrnvm></sel4slavebyadrpin>       |

|         |        | SA9 shall correspond to a programmable 1Bit slave address in case <sel2slavebyadrpin> or <sel2slavebyadrnvm>. SA8:7 is slave internal address bit.</sel2slavebyadrnvm></sel2slavebyadrpin>                |

|         |        | SA6:0 are optional address bits.                                                                                                                                                                          |

| REQ_108 | САР    | Capture mode; captures (freezes all sensor data channels) Optional functionality. If not implemented this bit position shall be fixed 0b.                                                                 |

|         |        | Allows to freeze/release all data channels under control of this bit. This allows to read sequentially different data channels while it is assured that the data of all channels is from same time stamp. |

Technical Specification

Page 29 / 36

**Rev 2.0**